How to improve the isolation of pin diode switch

PIN Diode Isolation Improvement

Four Key Technical Approaches

Device Structure Optimization

Fundamental improvements at semiconductor material level:

- Using wide bandgap materials (GaAs/SiC) to reduce reverse leakage current and maintain high isolation at elevated temperatures

- Increasing I-layer thickness while reducing doping concentration to minimize junction capacitance and suppress high-frequency signal leakage

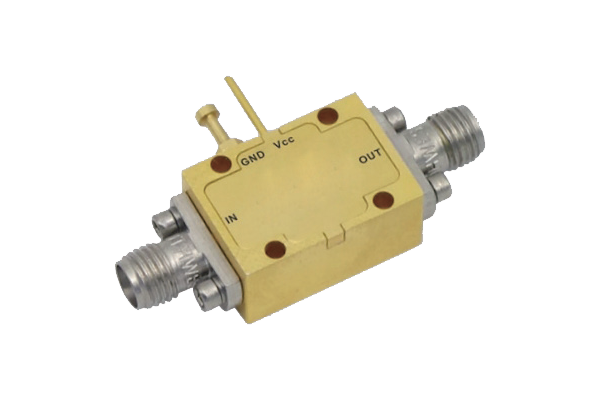

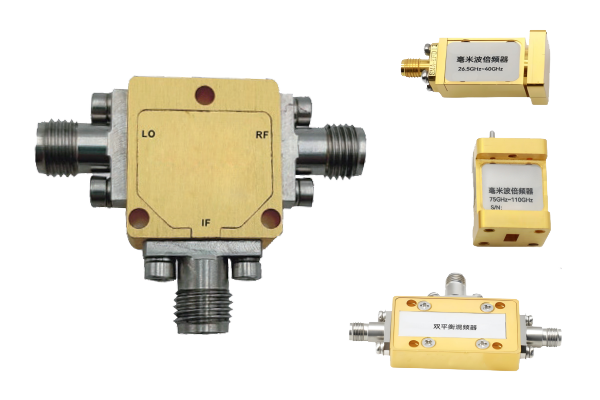

Circuit Design Improvement

Advanced topologies for signal isolation:

- Balanced bridge and multi-stage cascade topologies with symmetrical structures to cancel common-mode signals

- Series-connected switch arrays for stepwise signal attenuation

- Implementing λ/4 stubs and high-impedance matching networks to create port reflections that weaken leakage signals

Bias Control Techniques

Precision charge management strategies:

- Increasing reverse bias depth to fully deplete I-layer charges and minimize junction capacitance

- Applying carrier removal pulses during switch-off transitions to rapidly clear residual charges and reduce crosstalk

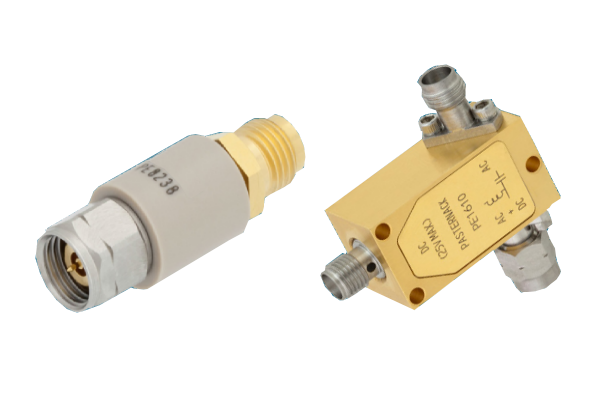

Packaging Process

Physical implementation enhancements:

- Increased signal line spacing with ground shielding layers to reduce parasitic coupling

- Flip-chip and monolithic integration to minimize bond wire parasitic inductance

- Hermetic ceramic/metal packaging to prevent moisture/contaminant intrusion and ensure long-term stability